Vivado报错集合

1 ERROR: [Common 17-49] Internal Data Exception:

这个错误通常表示在使用 vvdo 进行逻辑分析时出现了问题。错误信息表明,存在一个断言失败,即在获取探针数据时,数据不匹配。

2 Synth 8-5535

报错代码

1 | |

2.1 原因

普通IO输入的时钟信号必须要经过buffer才能驱动PLL

2.2 解决方法

将clocking wizard中的输入信号配置为 No Buffer

3 Warning:filegmt 56-199

3.1 解决方法

在Sources栏右键选择refresh hierarchy即可

4 Warning:CRITICAL WARNING: [filemgmt 56-176] Module references are not supported in manual compile order mode and will be ignored.

4.1 解决方法

将刷新层次结构的模式设置为自动更新和编译即可

5 [BD 41-237] Bus Interface property FREQ_HZ does not match between /M_AXIS_DATA_0(100000000) and /dds_compiler_0/M_AXIS_DATA(200000000)

引发这个报错的原因是IP核的时钟频率为200M,但是AXI4s的端口的频率为100M,因此将端口的频率设置为和IP核匹配的频率即可

6 vivado的各种设置无法保存

6.1 原因

“C:\Users\31651\AppData\Roaming\Xilinx\Vivado\2023.2\vivado.xml”这个文件里面存放了vivado的设置,例如最近打开的文件等

如果这些路径中有中文字符或其他vivado无法识别的字符,那么每次启动时vivado无法正常读取这些配置,就会重置这个文件,表现为重启vivado后所有配置全部丢失

6.2 解决方法

将含有中文字符的文件路径删除或者改成英语命名

7 [Common 17-180] Spawn failed: No error

7.1 导致原因

在 Vivado 中,报错信息 “[Common 17-180] Spawn failed: No error” 表示 Vivado 无法成功启动或创建某个进程,尽管没有明确的错误信息。这个错误通常发生在 Vivado 尝试启动外部进程或执行某些操作时,比如编译、生成比特流或启动仿真工具等。

7.2 TIMING #1 Critical Warning A primary clock top_i/clk_wiz_0/inst/clk_in 1 is created on an inappropriate pin top_i/clk_wiz_0/inst/clk_in 1. It is recommended to create a primary clock only on a proper clock source (input port or primitive output pin with no timing arc)

PS 输出 120 MHz 时钟的时候,真实输出的频率为 $125MHz$,因此在 PS 的时钟输出后级联了 clk_wiz 来转化时钟频率。综合后报错。

7.2.1 解决方法

由于 clk-wiz 输入端加入了 buffer,所以警告,只需要把输入设置为 no buffer 即可。

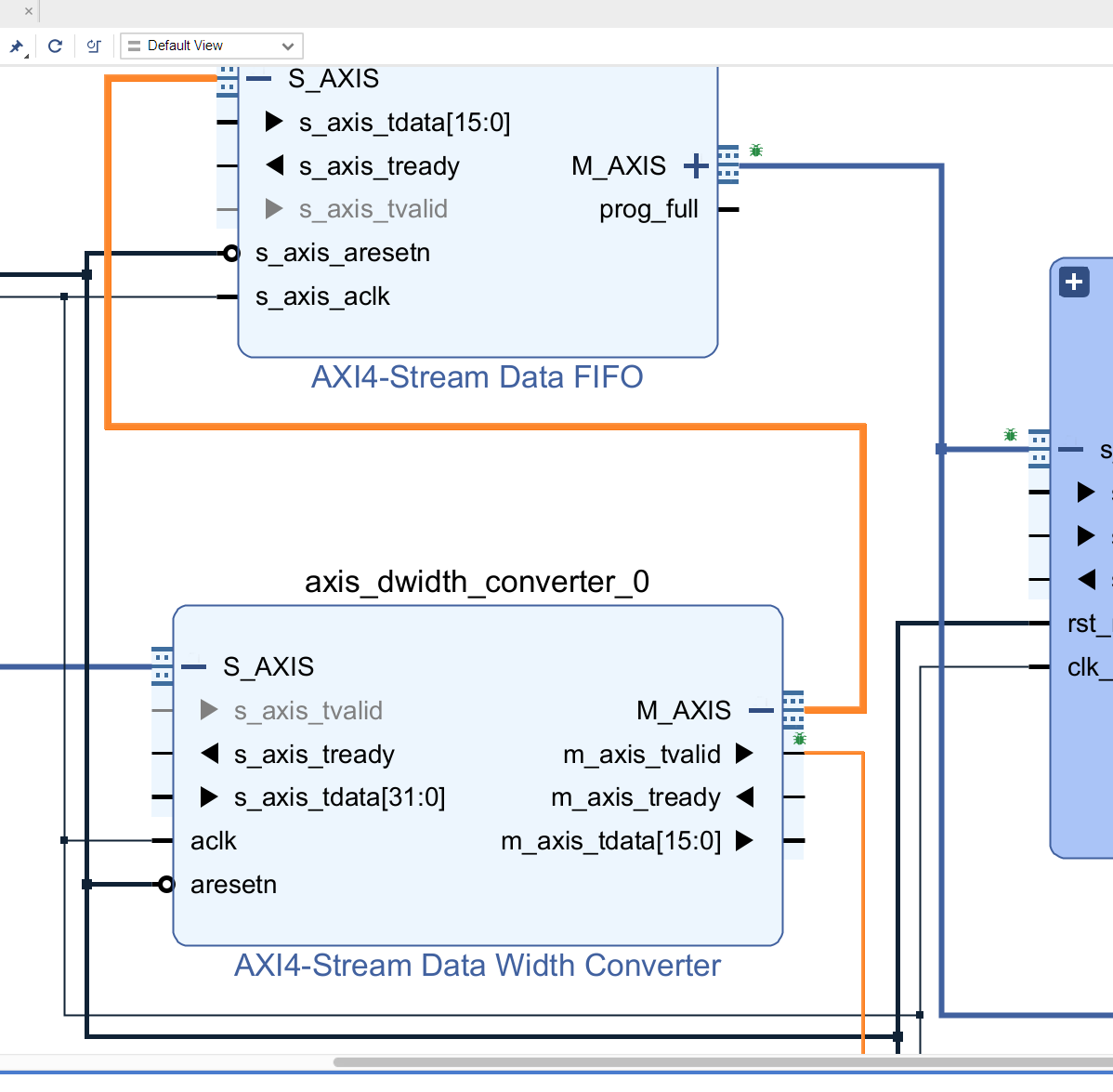

7.3 Debug 时不能将 axis 总线的某个信号接入到 ila,否则会导致下一个模块的这个信号无法联通

Vivado报错集合

https://www.moerjielovecookie.icu/2024/05/01/Vivado报错集合/