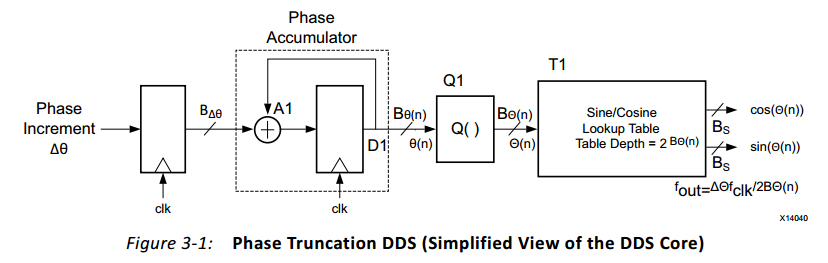

DDS内部结构

实现流程

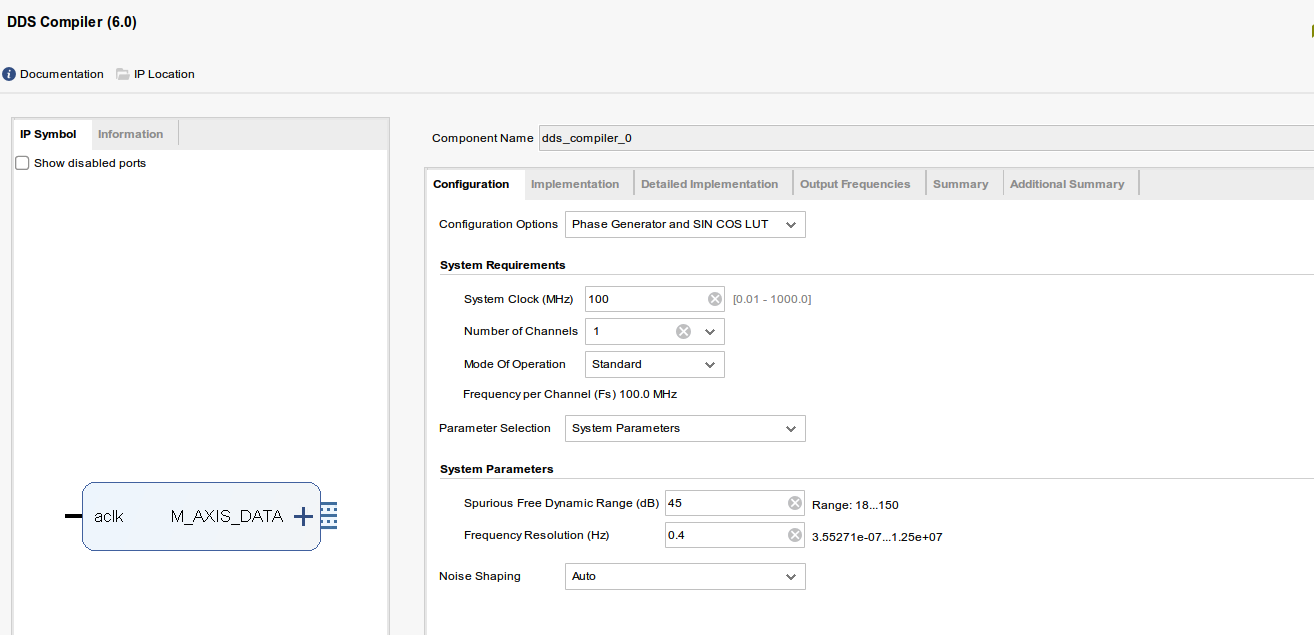

首先新建一个工程,创建bd文件,添加DDS Compiler核,此处不多赘述

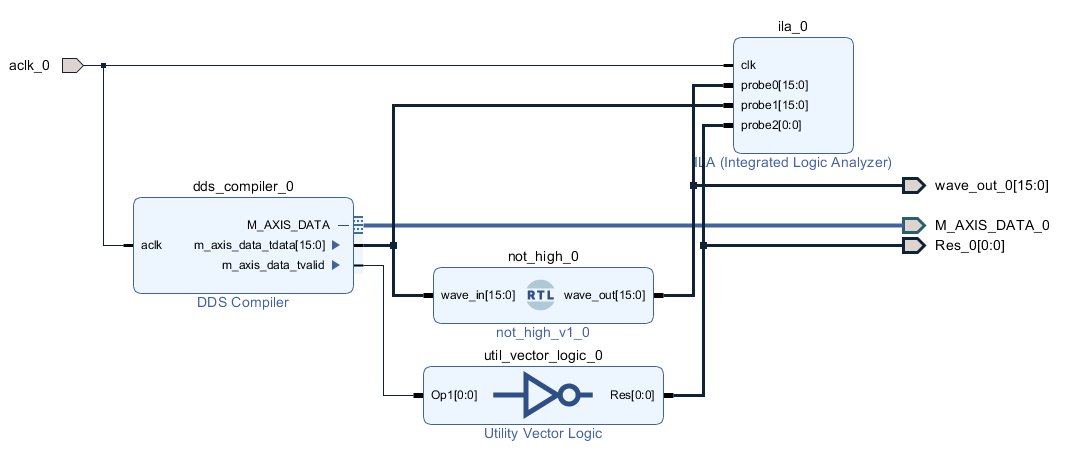

Block Design

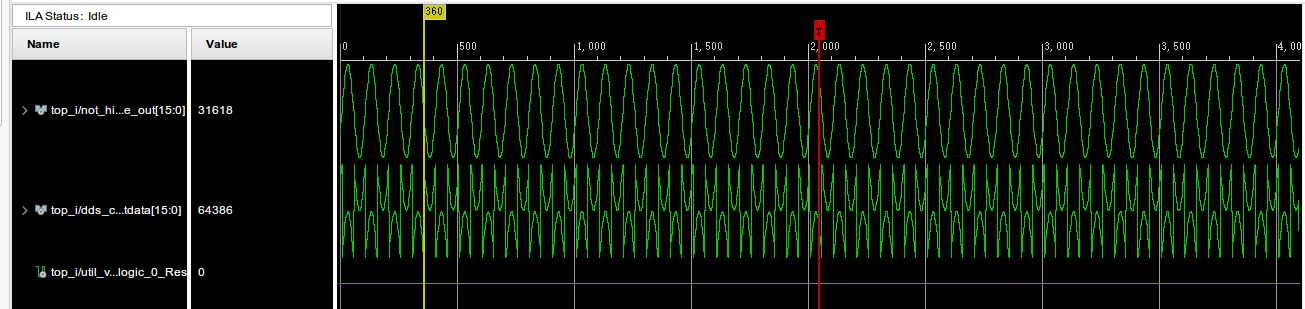

在观测输出的信号时,需要将最高位的信号取反,这样才能输出正弦波,否则输出的波形如下图所示

将tvalid信号取反是因为将这个信号接到了开发板的LED0上,led需要低电平才能点亮,因此将vld信号进行取反

Testbench

bd文件转化成的Verilog文件如下

1 | //Copyright 1986-2018 Xilinx, Inc. All Rights Reserved. |

针对顶层模块的输入输出设计如下testbench文件

1 |

|

Testbench语法

1. 输入信号声明使用reg,输出信号声明使用wire

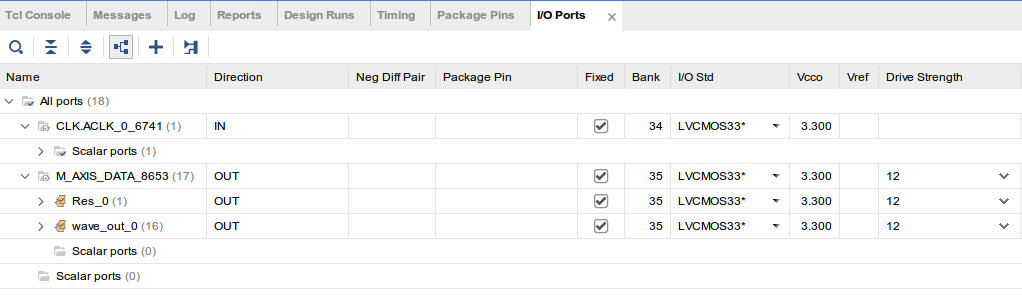

引脚约束

IO电平标准要设置为LVCMOS33,否则无法生成Bitstream文件

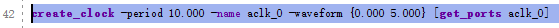

时序约束

添加完成后xdc文件会新增一行

- 本文作者: Moerjie

- 本文链接: https://moerjie.github.io/6c54dbd8628b/

- 版权声明: 本博客所有文章除特别声明外,均采用 MIT 许可协议。转载请注明出处!