AXI DMA+AXI-S FIFO回环学习

1 DMA 简介

DMA 是现代计算机的特色之一,是硬件实现存储器与存储器、存储器与 I/O 设备之间直接进行高速数据传输的内存技术,它允许不同速率的设备进行沟通,而不需要依靠 CPU 的中断负载。

如果不使用 DMA,那么 CPU 需要从数据源把每一个片段的数据复制到寄存器中,这个过程会一直占用 CPU 的资源。当使用 DMA 时,CPU 向 DMA 发送一个存储传输请求,当 DMA 控制器收到请求时就会将数据从源地址搬运到目的地址,搬运过程中不消化 CPU 的资源,当传输完成后 DMA 控制器以中断的方式通知 CPU。

为了发起传输事务,DMA 控制器必须有:

- 源地址

- 目的地址

- 传输长度

DMA 存储传输的过程如下: - 处理器向 DMA 控制器发送一条 DMA 命令

- DMA 控制器把数据从外设传输到存储器或从存储器搬运到存储器,而让 CPU 腾出手来做其它操作

- 数据传输完成后,DMA 控制器向 CPU 发出一个中断,来通知处理器 DMA 传输完成

ZYNQ 提供两种 DMA,一种是集成在 PS 中的硬核 DMA,一种是 PL 中的软核 AXI DMA IP。

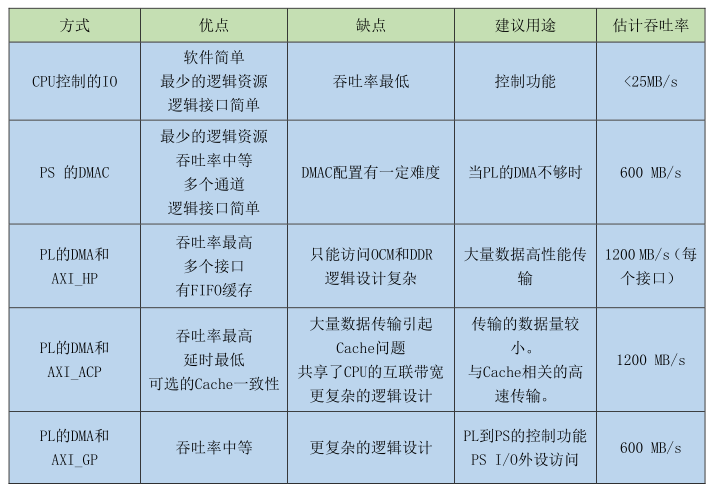

各种接口方式的比较如下:

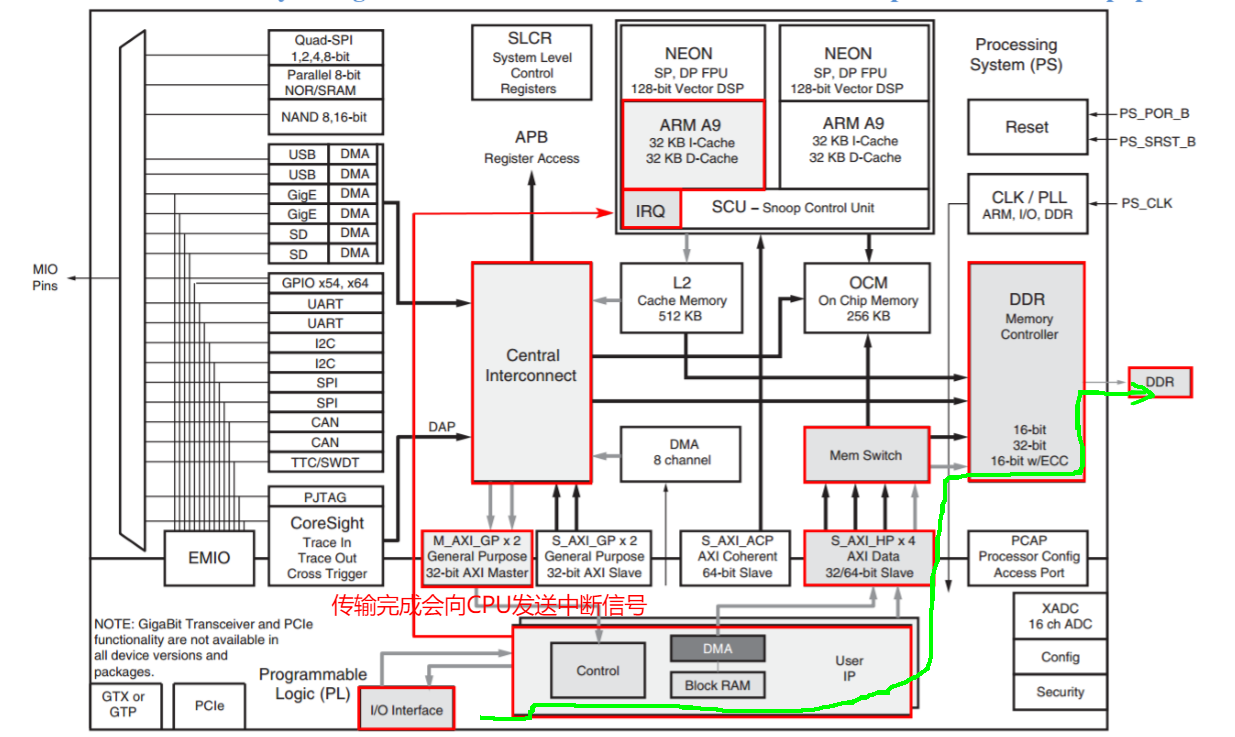

PL 的 DMA 和 AXI_HP 接口的传输适用于大量数据的高性能传输,带宽高,传输方式的拓扑图如下:

1.1 AXI DMA IP

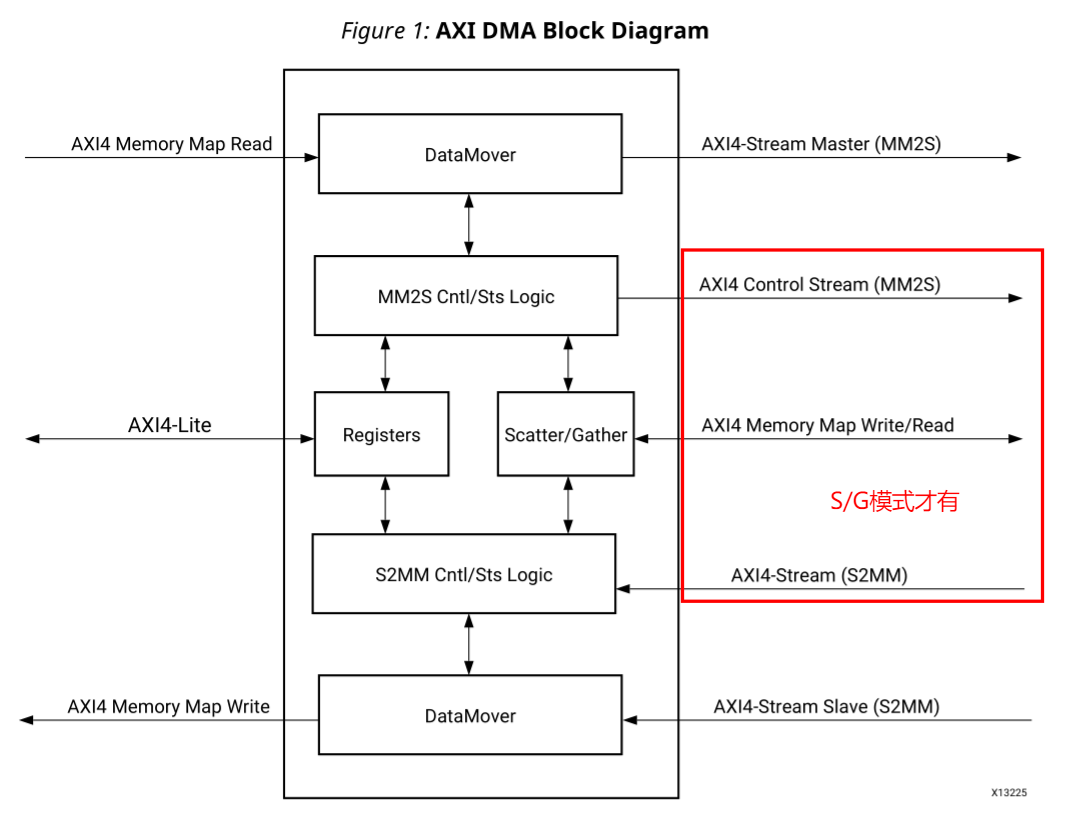

AXI Direct Memory Access(AXI DMA)IP 核在 AXI 4 内存映射和 AXI 4-Stream IP 接口之间提供高带宽直接储存访问。

AXI DMA 用到了三种总线。AXI 4-Lite 用于对寄存器进行配置,AXI 4 Memory Map 总线用于读写 DDR 中的数据,AXI 4 Stream 总线用于 AXI DMA 对外设数据的读写,其中 AXI 4 Stream Master(MM 2 S,Memory Map to Stream)接口用于向 PL写入数据,AXI 4-Stream Slave (S 2 MM,Stream to Memory Map) 接口用于从 PL读取数据。

AXI DMA 提供 3 种模式,分别是 Direct Register 模式、Scatter/Gather 模式和 Cyclic DMA(循环 DMA)模式,常用的是 Direct Register 模式。

Direct Register DMA 模式即 Simple DMA 模式。Direct Register 模式提供了一种配置,用于在 MM 2 S 和 S 2 MM 通道上执行简单的 DMA 传输。Simple DMA(简单 DMA)允许应用程序在 DMA 和 Device 之间定义单个事务。它有两个通道:一个从 DMA 到 Device,另一个从 Device 到 DMA。这里有个地方需要大家注意下,在编写 Simple DMA(简单 DMA)代码时必须设置缓冲区地址和长度字段以启动相应通道中的传输。(其中 PL 对应 Device)

1.1.1 Vivado 中的 IP 配置

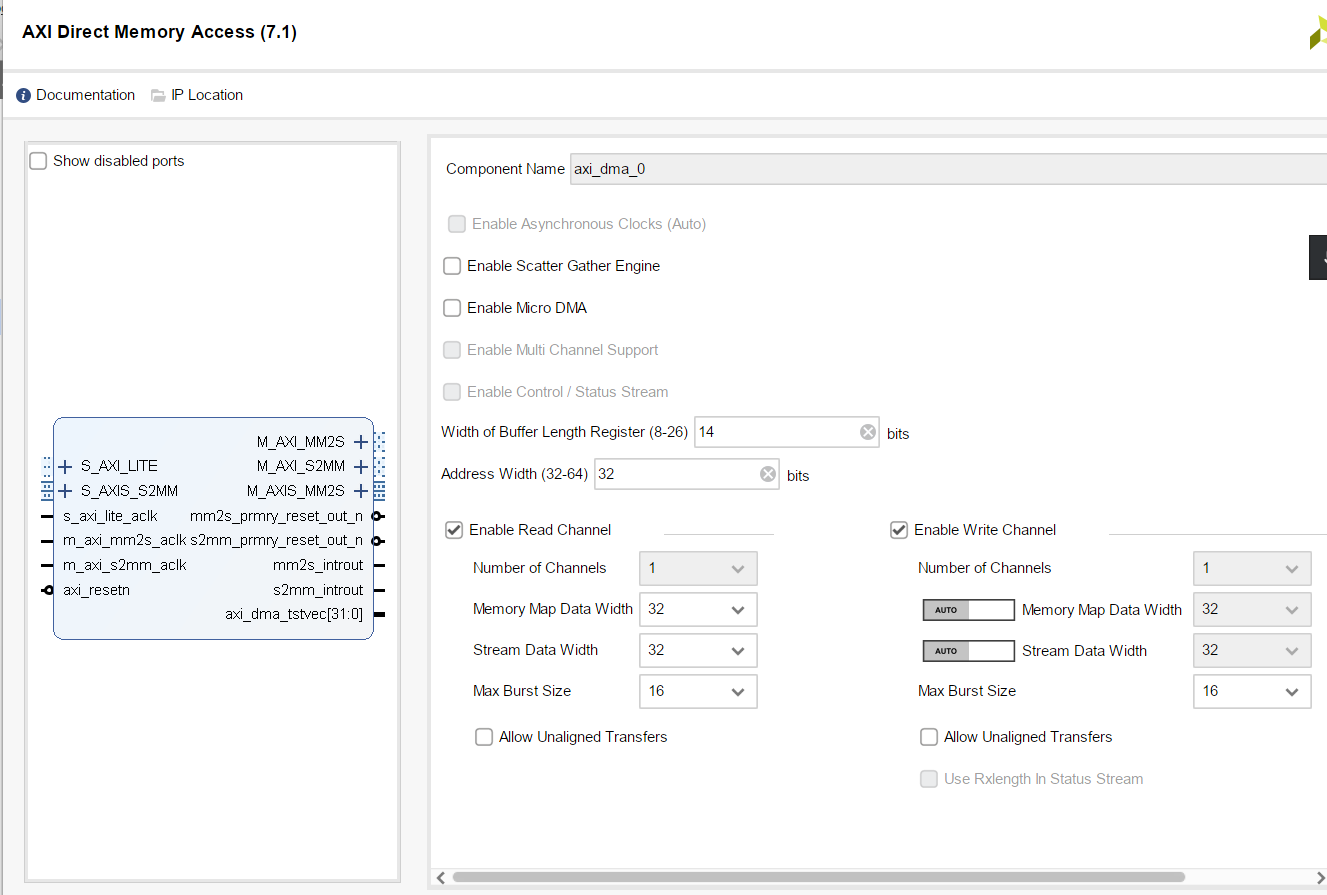

Enable Scatter Gather Engine

选中此选项可启用 Scatter Gather 模式操作,并在 AXI DMA 中包含 Scatter Gather Engine。取消选中此选项可启用 Direct Register 模式操作,但不包括 AXI DMA 中的 Scatter Gather Engine。禁用 Scatter Gather Engine 会使 Scatter/Gather Engine 的所有输出端口都绑定为零,并且所有输入端口都将保持打开状态。此处我们取消勾选 Enable Scatter Gather Engine

Enable Micro DMA

使能后会生成高度优化的 DMA,资源消耗较少,用于极少量数据的传输

Width of Buffer Length Register

该选项配置了 AXI DMA 单次最大能搬运多少个字节,字节数

Address Width (32 - 64)

指定地址空间的宽度,可以是 32 到 64 之间的任意值

Enable Read Channel

开启 AXI DMA 的读通道 MM 2 S,相关配置如下:

- Number of Channels:指定通道数。保持默认值 1

- Memory Map Data Width:AXI MM 2 S 存储映射读取数据总线的数据位宽。有效值为 32、64、128、256、512 和 1024。此处保持默认值 32

- Stream Data Width:AXI MM 2 S AXI 4-Stream 数据总线的数据位宽。该值必须小于或等于 Memory Map Data Width。有效值为 8、16、32、64、128、512 和 1024。此处保持默认值 32

- Max Burst Size:突发分区粒度设置。此设置指定 MM 2 S 的 AXI 4-Memory Map 侧的突发周期的最大值。有效值为 2、4、8、16、32、64、128 和 256

- Allow Unaligned Transfers:启用或禁用 MM 2 S 数据重新排列引擎(Data Realignment Engine,DRE)。选中时,DRE 被使能并允许在 MM 2 S 存储映射数据路径上数据重新对齐到 8 位的字节水平。对于 MM 2 S通道,则从内存中读取数据。如果 DRE 被使能,则数据读取可以从任何缓冲区地址字节偏移开始,并且读取数据被对齐,使得第一个字节读取是 AXI 4-Stream 上的第一个有效字节输出

Enable Write Channel

开启 AXI DMA 的写通道 S 2 MM,相关配置同上

2 Vitis 工程解析

2.1 头文件引用和宏定义

1 | |

#define DDR_BASE_ADDR XPAR_AXI_7SDDR_0_S_AXI_BASEADDR 重新定义了 DDR 3 的基址.。数据读写的基址为 #define MEM_BASE_ADDR (DDR_BASE_ADDR + 0x01000000) // 0x01100000 AXI DMA 读取数据的起始地址为 #define TX_BUFFER_BASE (MEM_BASE_ADDR + 0x00100000) // 0x01200000,写入地址为 0x01400000

2.2 定义函数和声明相关的 instance 和 flag 变量

1 | |

2.3 Main 函数

1 | |

Tries 为测试回环的次数

2.4 函数的实现

1 | |