ZYNQ-IP-AXI-GPIO

AXI GPIO 可以将 PS 端的一个 AXI 4-Lite 接口转化为 GPIO 接口,并且可以被配置为单端口或双端口,每个通道的位宽可以独立配置。

通过使能三态门可以将端口动态地配置为输入或输出。

AXIGPIO 是 ZYNQ PL 端的一个 IP 核,可以将 AXI-Lite Master 转为 GPIO,并且一个 AXI-Lite 接口可以通过 AXI interconnect 模块控制多个 AXI-GPIO。

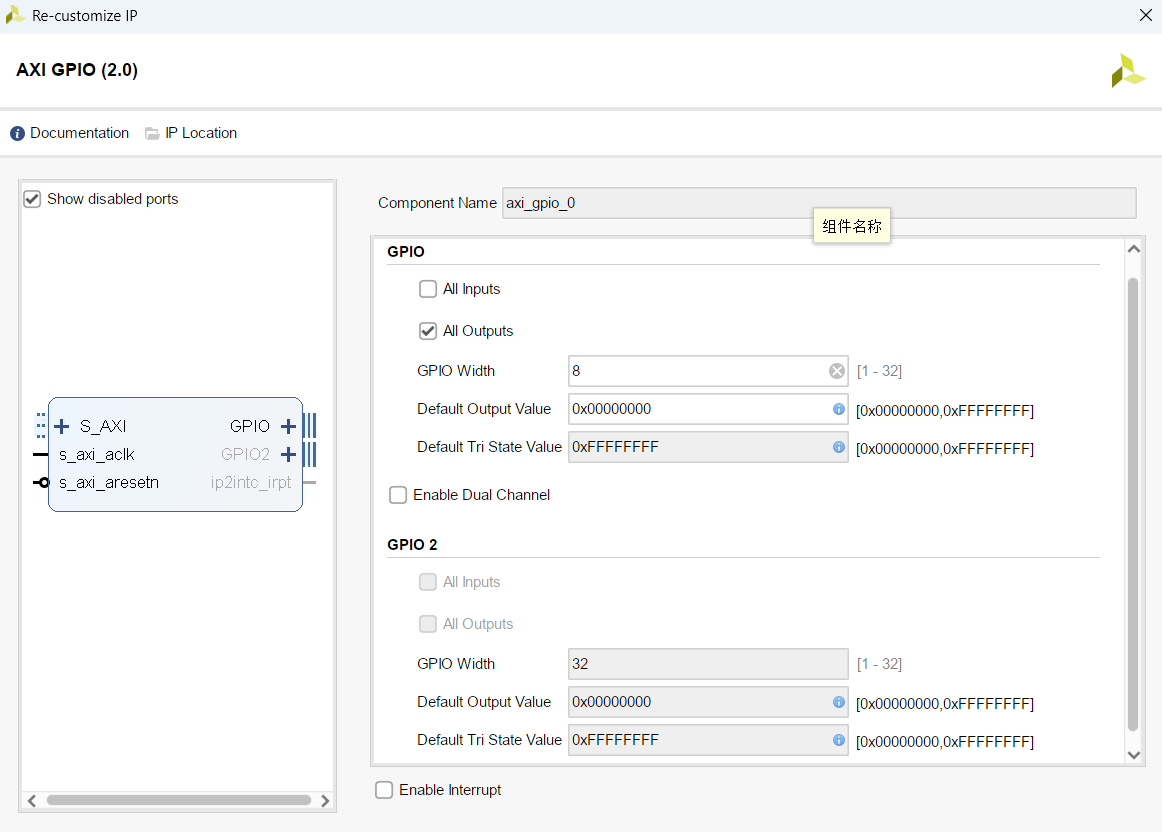

AXI-GPIO IP 设置

最大时钟频率

AXI GPIO 设置

默认为单通道。GPIO 的方向在这里设置了以后就不能在 vitis 中设置 GPIO 的方向。

中断属于 PL 对 PS 的中断,需要在 ZYNQ 7 Processing System 中勾选

生成的 vitis 的代码中,xparameters.h 中的 id 默认从 ID 0 开始,不管 vivado 这边的 AXI-GPIO 的序号是从 0 开始还是从 1 开始。

[!note]

- GPIO 只能使能整个通道中断,无法单独使能通道中的某个引脚中断

中断类型只能设置为上升沿或高电平

AXI-GPIO 相关代码

初始化

1 | |

设置输入输出方向

1 | |

GPIO 读写

1 | |

ZYNQ-IP-AXI-GPIO

https://www.moerjielovecookie.icu/2025/01/20/ZYNQ-IP-AXI-GPIO/