ZYNQ中的GPIO

GPIO 原理

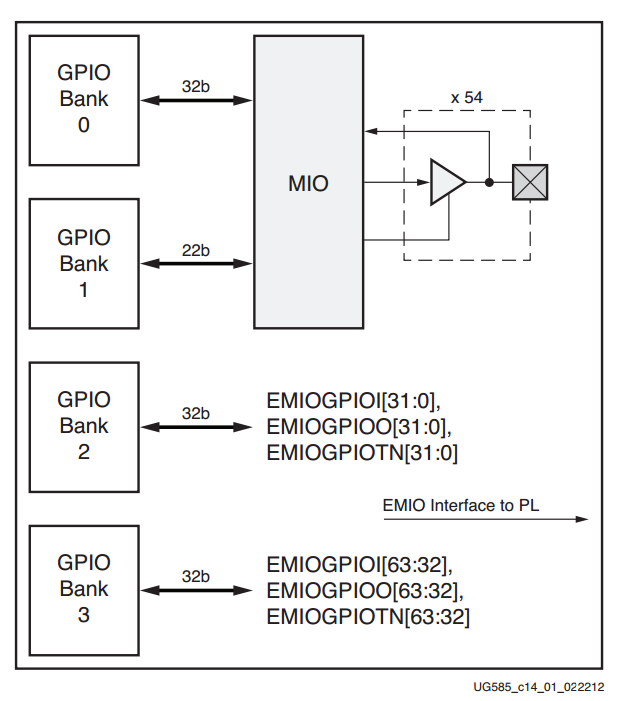

GPIO 通过 MIO 提供 54 路接口,其中 16 路位于 bank 500,剩余位于 bank 501。还通过 EMIO 接口提供从 PL 来的 64 路输入和 128 路输出。GPIO 控制和状态寄存器内存映射在基址

ZYNQ 的 GPIO 引脚分为 4 个 bank,共有 118 个 GPIO。

GPIO 内部结构

从图中可以看到 GPIO 有三个功能:输入、输出、中断。

其中 MIO 7 和 9 只能做输出。

一组寄存器只能控制一个 GPIO bank 的所有引脚。

器件引脚的 GPIO 控制

输入/输出寄存器

| 寄存器名称 | 说明 |

|---|---|

| DATA_RO | GPIO引脚的值存储在此寄存器中,无论GPIO被配置为输入或输出,都可以通过读此寄存器得到GPIO引脚的值。 因为是只读寄存器(对软件来说),软件向此寄存器的写入操作将被忽略。 |

| DATA | 输出数据寄存器,当GPIO被配置为输出才起作用,此寄存器中的值就是输出到引脚的值。 向此寄存器写入就是在设置GPIO的输出值, 读此寄存器将返回GPIO前一时刻的输出值,而不是现在的值。 |

| MASK_DATA_LSW | Mask Data Least Significant Words,输出数据低16位掩码寄存器,此寄存器只有低16位有效, 对应位为1表示DATA寄存器低16位中对应位的值可以更改, 若不为1,则表示DATA寄存器低16位中对应位保持原值 |

| MASK_DATA_MSW | Mask Data Most Significant Words,输出数据高16位掩码寄存器, 功能同MASK_DATA_LSW,只是它对应DATA寄存器高16位 |

| DIRM | Direction Memory,方向寄存器,默认为0表示输入,设为1表示输出 注意,即使DIRM为1,软件也可以像输入一样去读此引脚的电平 |

| OEN | Output Enable,输出使能寄存器, 仅当DIRM为0时有效,为1表示输出使能, 为0表示输出不使能,此时对应引脚上的值为三态值 |

中断控制寄存器

| 寄存器名称 | 说明 |

|---|---|

| INT_TYPE | Interrupt Type 中断类型寄存器, 控制GPIO中断是电平触发还是边缘触发 |

| INT_POLARITY | Interrupt Polarity 中断极性寄存器 控制GPIO中断是低电平/下降沿有效,还是高电平/上升沿有效 |

| INT_ANY | Interrupt Any,双边沿寄存器, 仅当INT_TYPE为边沿触发时,此寄存器才有效,控制是否双沿均可触发中断 |

| INT_STAT | Interrupt State,中断状态寄存器, 此寄存器的值会被与之相连的INT State D触发器读取 D触发器存储中断状态,软件通过读此D触发器输出来判断中断是否发生, 清除此D触发器来清除中断状态 |

| INT_MASK | Interrupt Mask,中断掩码寄存器, 显示当前哪些位被屏蔽,哪些位启用 |

| INT_DIS | Interrupt Disable,中断失效寄存器, 向该寄存器的任何位写入 1 都会屏蔽该中断信号。 从该寄存器读取会返回不可预测的值 |

| INT_EN | Interrupt Enable,中断使能寄存器 向该寄存器的任何位写入 1,可以启用/解除中断信号的掩码。 从该寄存器读取将返回一个不不可预测的值 |

GPIO 的中断号为 ==52==,中断优先级是固定的,无需配置 GPIO 的中断优先级。GPIO 所有引脚共享同一个中断,即使能两个引脚的中断的话,软件无法判断中断来自哪个引脚。

EMIO 和 MIO

MIO,Multiuse I/O,复用输入/输出,对应 PS 端的可配置的多功能引脚。

EMIO,Extent MIO,对应 PL 端的可配置多功能引脚。

MIO 是外设的基本引脚,由于 MIO 的引脚数量较少,ZYNQ 也提供 EMIO 接口作为 MIO 的扩展,外设通过 EMIO 接口连接到 PL 端的引脚,来实现和 MIO 几乎相同的功能。

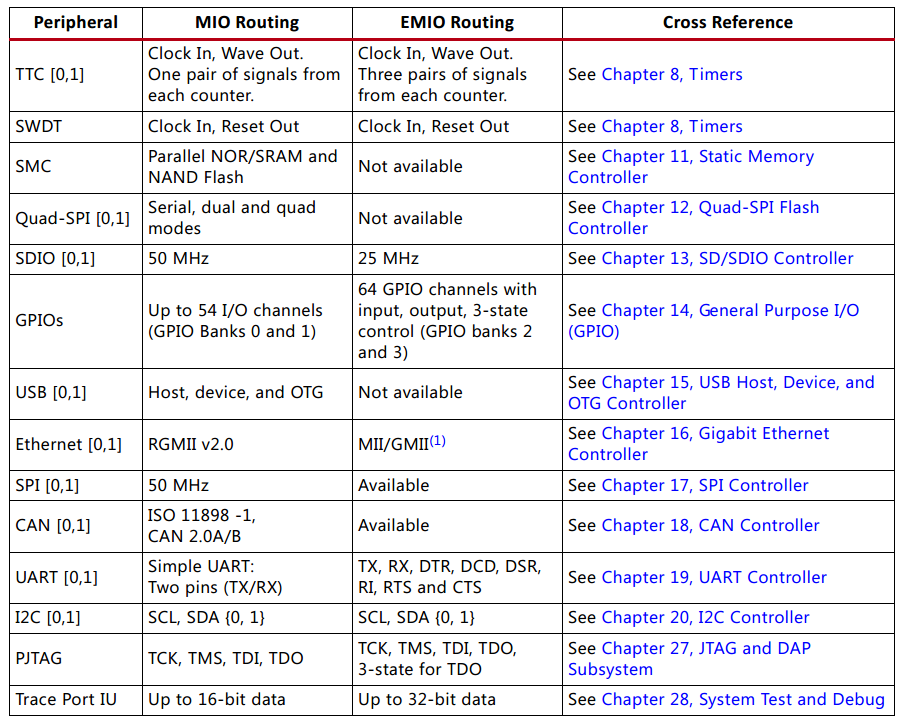

MIO 和 EMIO 的不同点如下:

- MIO 对于 PL 端是透明的,PL 无法读取 MIO 引脚上的电平;PS 端可以通过 EMIO 与 PL 端通信。

- 外设与 MIO 是固定搭配的,初始化时要根据开发板原理图来选择引脚约束。EMIO 相对灵活,引脚可以任意指定,通过 xdc 文件约束指定到 PL 端的某个引脚。

- 因为 MIO 引脚更靠近外围电路,相较于 EMIO,一些外设使用 MIO 的性能更好,还有一些外设只能使用 MIO。

MIO bank 和封装的 bank 的区别与联系

MIO 分为 Bank 0 和 Bank 1,Bank 0 是封装 Bank 500 中的部分引脚,Bank 1 是封装的 bank 501 的部分引脚。

Bank 0 包含 MIO 015 共 16 个 MIO,bank 1 包括 MIO 1653 共 38 个 MIO,总共有 54 个 MIO。EMIO 一共有 64 个。

ZYNQ中的GPIO

https://www.moerjielovecookie.icu/2025/01/20/ZYNQ中的IO/