1 Matlab处理数据并将其写入txt文件

1

2

3

4

5

6

7

|

pre_RS_data=dec2bin(simDataIn,8);

fid=fopen("F:\FPGA\Xilinx_vivado\project\dvbstestbench\dbvs\matlab\pre_RS_data.txt","wt");

for i=1:n*nMessages

fprintf(fid,"%s\n",pre_RS_data(i,1:8));

end

fclose(fid);

|

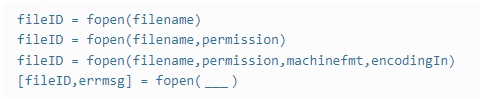

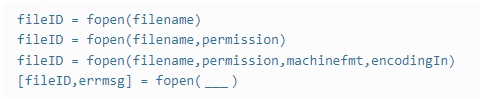

使用fopen函数获取文件id,fopen的语法如下

其中permisson为文件访问类型,有以下几种权限

'r' |

打开要读取的文件。 |

'w' |

打开或创建要写入的新文件。放弃现有内容(如果有)。 |

'a' |

打开或创建要写入的新文件。追加数据到文件末尾。 |

'r+' |

打开要读写的文件。 |

'w+' |

打开或创建要读写的新文件。放弃现有内容(如果有)。 |

'a+' |

打开或创建要读写的新文件。追加数据到文件末尾。 |

'A' |

打开文件以追加(但不自动刷新)当前输出缓冲区。 |

'W' |

打开文件以写入(但不自动刷新)当前输出缓冲区。 |

💡 要以文本模式打开的话,要附加’t’

2 Vivado中testbench写法

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

| `timescale 1ns/1ps

module top_tb();

reg clk;

reg rst_n;

reg [7:0]SEQ_IN_0;

reg [7:0] data_mem[1:1020];

reg [31:0] i;

wire BIN_OUT;

wire ce_out;

wire locked;

initial begin

clk=1'b0;

rst_n=1'b0;

#100

rst_n=1'b1;

end

always #5 clk=~clk;

initial begin

$readmemb("F:/FPGA/Xilinx_vivado/project/dvbstestbench/dbvs/matlab/pre_RS_data.txt",data_mem);

end

initial begin

i=1;

forever @(posedge clk) begin

if(i<1020) begin

i=i+1;

end

else

i=1;

end

$display("%s",data_mem[i]);

end

always @(posedge clk) begin

SEQ_IN_0<=data_mem[i];

end

top_wrapper top_wrapper_u0(

.clk_0 (clk),

.rst_n_0 (rst_n),

.SEQ_IN_0(SEQ_IN_0),

.BIN_OUT_0 (BIN_OUT),

.ce_out_0 (ce_out),

.locked_0 (locked)

);

endmodule

|

💡 直接在文件夹内部复制的文件路径是\,但是testbench中要将所有反斜杠改为/,否则无法读取txt文件